I.MẠCH CỘNG

1.Mạch cộng nửa

Gọi : A là số được cộng

B là số cộng

S là tổng của A và B

C là số nhớ ra từ phép cộng

Trước hết để đơn giản, xét mạch cộng nhị phân 1 bit

Với tổ hợp 4 trạng thái logic của A và B thì trạng thái logic ngõ ra S và C như sau:

Hình 2.3.7 Cộng nửa

Rút gọn biểu thức logic ta có

S = AB + AB

C = AB

Nhận thấy S là ngõ ra của cổng EXOR 2 ngõ vào A và B; còn C là ngõ ra của cổng AND

Từ đây vẽ được cấu trúc logic của mạch :

Hình 2.3.8 Mạch cộng nửa

Đây là mạch cộng nửa hay cộng chưa đủ (haft adder : HA) vì chưa có số nhớ ban đầu của phép cộng trước đó.

2.Mạch cộng đủ

Bây giờ giả sử mạch đã thực hiện phép cộng lần đầu rồi nên được tổng là S0 và số nhớ C0, nếu tiếp tục cộng lần 2 khi trạng thái logic của A và B thay đổi thì S không chỉ là tổng của A và B mà gồm cả C0 trước đó. Khi này ta có mạch cộng đủ: full adder (FA)

Hình 2.3.9 Cộng đủ

Rút gọn biểu thức ta được

S = C0 Å (A Å B)

C = AB + (A Å B)

Cấu trúc của mạch logic sẽ là :

Hình 2.3.10 Mạch cộng đủ

Nhận thấy rằng : FA thực ra bao gồm trong nó 2 HA và cổng OR ở ngõ ra cho số nhớ C

Cả 2 mạch HA và FA ở trên mới chỉ làm phép cộng 1 bit

3.Cộng nhiều bit

a)Cộng song song

Bây giờ nếu 2 số cộng có nhiều bit hơn thì cách cộng cũng sẽ tương tự : trước hết cộng 2 bit LSB để cho bit tổng (LSB). Số nhớ được đưa tới để cộng chung với 2 bit kế tiếp bit LSB để cho bit tổng ở hàng kế tiếp cho đến phép cộng cuối cùng giữa 2 bit MSB để được bit tổng ở hàng đó, số nhớ khi này trở thành bit LSB của tổng

Hình sau sẽ minh hoạ rõ ràng hơn mạch cộng nhiều bit (4 bit)

Hình 2.3.11 Cộng 4 bit

Đây là một mạch cộng song song vì các hàng được cộng cùng một lúc tuy nhiên như cấu trúc mạch ở trên thì các bit ra của tổng không phải là đồng thời bởi vì các phép cộng ở các bit cao thì chậm hơn do phải chờ bit nhớ ở phép cộng trước đưa tới. Tức là đã có trì hoãn làm giảm tính đồng bộ của mạch. Nếu thêm vào mạch cho phép cung cấp sẵn các bit nhớ để phục vụ cho các phép cộng ở các hàng được cùng lúc thì sẽ khắc phục được điểm này. Với công nghệ tích hợp cao, việc thêm mạch cung cấp sẵn các bit nhớ trở nên dễ dàng hơn khi đó mạch trở thành mạch cộng có số nhớ nhìn trước.

Một số IC làm phép cộng toàn phần được kể ra ở đây là

♦ 7480 (1bit), 7482 (2bit), 7483/LS83/283 (4bit)

Ví dụ : xét qua IC 74LS83

Hình 2.3.12 Kí hiệu khối và chân ra 74LS83

Trong đó 2 số 4 bit vào là A4A3A2A1 và B4B3B2B1

Số nhớ ban đầu là C0

Vậy tổng ra sẽ là C4S4S3S2S1, với C4 là số nhớ của phép cộng

Ta cũng có thể nối chồng IC cộng lại với nhau để cho số bit gấp đôi. Khi đó bit MSB (C4) của tầng đầu được nối tới ngõ vào nhớ ban đầu (C0) của tầng sau.

Hình 2.3.13 Mạch logic của 74LS83

Bảng sự thật của mạch cộng 4 bit 74LS83 b)Cộng nối tiếp

b)Cộng nối tiếp

Ngoài cách cộng song song như đã thấy ở trên, còn một dạng mạch cộng số nhiều bit nữa gọi là mạch cộng nối tiếp. Khi này 2 bit LSB của các số được cộng trước, bit LSB của tầng được đưa ra 1 ghi dịch còn số nhớ sẽ quay trở về cộng chung với 2 bit kế tiếp bit LSB và cứ vậy cho đến 2 bit cuối cùng được cộng. Mạch ghi dịch ngõ ra dịch chuyển sang phải qua mỗi lần cộng sẽ cho ra kết quả cộng số nhớ cuối cùng trở thành bit MSB của tổng ra. Rõ ràng mạch thực hiện phép tính chậm hơn so với cộng song song, nó cũng cần 1 xung nhịp để giữ cho các mạch làm việc động bộ

Hình 2.3.14 Mạch cộng 4 bit nối tiếp

II.MẠCH TRỪ

1.Mạch trừ nửa và trừ đủ

Cũng gồm 2 loại mạch trừ nửa hay chưa đủ : haft subtractor (HS) và trừ đủ hay còn gọi là trừ bán phần : full subtractor (FS) (khi này cần bit mượn Bi trước tham gia vào phép tính)

Phép trừ thực ra là phép cộng với số âm. Để có số âm của 1 số ta lấy bù 1 của số đó, còn khi thực hiện mạch thì đó là cổng đảo

Hình 2.3.15 là mạch trừ HS và bên cạnh là bảng trạng thái

|

|

|

| Hình 2.3.15 Mạch trừ nửa, bảng trạng thái và mạch logic | ||

Còn hình 2.3.17 là mạch trừ FS cùng bảng trạng thái hoạt động ở bên cạnh

hình 2.3.17 Mạch trừ đủ

Về cấu trúc mạch trừ cũng tương tự mạch cộng chỉ khác là số bị trừ B cần phải qua cổng đảo khi thực hiện AND với số trừ A để cho số mượn R. Mạch trừ FS cũng gồm 2 mạch trừ HS và cổng OR ở ngõ ra cho số mượn B0

Hình 2.3.18 Mạch trừ hết

2.Mạch trừ nhiều bit

Với mạch trừ nhị phân nhiều bit, cũng có thể thực hiện song song các mạch cộng FS từng bit nhưng các bit của số bị trừ cần được đảo, số nhớ của tầng cuối cần đem về bit nhớ ban đầu của tầng đầu. Hình minh hoạ cho mạch trừ nhị phân 4 bit

Hình 2.3.19a Mạch trừ 4 bit song song |

|

3.Mạch cộng trừ kết hợp

Bây giờ nếu thêm vào một số cổng logic cần thiết ta đã có 1 mạch có thể cộng hay trừ tuỳ theo ngõ vào điều khiển CT.Khi CT = 0, các cổng EXOR có 1 ngõ ở thấp nên cho số B qua không bị đảo, tức là mạch thực hiện phép cộng.Khi CT = 1, các cổng EXOR có 1 ngõ ở cao nên hoạt động như 1 cổng NOT, số B bị đảo, khi này mạch thực hiện phép cộng A + (-B) tức là phép trừ.Co3 là bit LSB của tổng được vòng trở lại (qua cổng AND) về Ci0; sẽ cho phép cộng nhiều bit.

Hình 2.3.21 Mạch cộng trừ dùng bù 1

Ngoài cách dùng bù 1, ta cũng có thể dùng bù 2 (lấy bù 1 rồi cộng thêm 1) để thực hiện phép toán trừ nhị phân kể cả số có dấu. Cách này được sử dụng phổ biến ở VXL và máy tính.Hình 2.3.22 là mạch cộng trừ 2 số 4 bit dùng bù 2. Để ý là mạch khá giống như nó ở cách dùng bù 1 nhưng bit nhớ ra cuối cùng không cần đem về tầng đầu. Tổng hay hiệu ra ở dạng bù 2, muốn lấy đúng kết quả thì phải chuyển trở lại.

Khi đó mạch cộng trừ nhị phân 4 bit dùng bù 2 sẽ như sau :

Hình 2.3.22 Mạch cộng trừ dùng bù 2

III.CỘNG TRỪ BCD

1 Cộng 2 số BCD

Số BCD thực ra cũng là số nhị phân n bit nhưng chỉ có 10 tổ hợp trạng thái từ 0000 đến 1001 (biểu thị số thập phân tương ứng là từ 0 đến 9) nên cách cộng cũng tương tự như cổng số nhị phân nhiều bit. Tuy nhiên khi tổng vượt quá 1001 thì tức là tổng đó không còn là số BCD nữa, do đó ta phải cộng tổng với 0110 (số 610) để cho tổng mới là số BCD đồng thời số nhớ chính là hàng cao hơn của tổng.

Ví dụ như cộng 2 số BCD sau:

Hình 2.3.23 Mạch cộng 2 số BCD 1 bit

2 số cần cộng là A3A2A1A0 và B3B2B1B0 cho tổng là C3S4S3S2S1 (C3 là hàng chục nếu có).

Nếu tổng đầu vượt quá 9 ( từ 10 đến 18) thì các cổng logic sẽ cho phép xác định hàng chục đồng thời tổng này phải được cộng thêm 6 ở tầng 74LS83 thứ 2 để cho tổng cuối cùng ở dạng BCD.

Nếu tổng không vượt quá 9 (vẫn là số BCD) thì tổng hàng chục không có nên 74LS83 thứ 2 sẽ cộng tổng này với 0, tổng ra không có gì thay đổi.

Ta có thể ghép nhiều mạch cộng ở trên để có mạch cộng 2 số BCD nhiều bit, khi đó chỉ việc nối ngõ ra hàng chục của tầng đầu tới ngõ vào số nhớ Ci của tầng sau là được.

2.Trừ 2 số BCD

Với phép trừ BCD, ta phải lấy bù 9 của số trừ rồi mới làm phép cộng lại với số bị trừ. Lấy bù 9 của 1 số tức là lấy 9 trừ đi số đó. Ở chương 1 có nói rõ hơn về phép trừ BCD

Ví dụ về phép trừ BCD : 9 – 5 và 2 – 6

Hình 2.3.24 Mạch trừ 2 số BCD 1 bit

IV.MẠCH NHÂN CHIA

1.Mạch nhân 2 số nhị phân

Về nguyên lí, đó là phép cộng nhiều lần. Cách nhân 2 số nhị phân xin xem lại chương 1. Mạch ở hình 2.3.25 minh hoạ cho mạch nhân 2 số nhị phân 4 bit A và B. Mạch gồm ghi dịch 4 bit để chứa số được nhận A, ghi dịch 5 bit để chứa số nhân B, ghi dịch 6 bit để chứa kết quả nhân (còn gọi là bộ tích luỹ : accumulator). 5 cổng And sẽ tạo tích từng phần của các cặp bit và 6 bộ cộng toàn phần để tạo tích cuối và số nhớ tương ứng.

Hình 2.3.25 Cấu trúc 1 mạch nhân 2 số nhị phân

Ví dụ về phép nhân 2 số A = 1101và B = 1011:

Số nhân (A): 1101 (1310)

Số bị nhân B : 1011 (1110)

Tích 1101

từng 1101

phần 0000

1101

Tích cuối : 10001111 (14310)

2.Mạch chia 2 số nhị phân

Còn với mạch chia 2 số nhị phân, nguyên tắc là trừ liên tiếp để cho kết quả, bạn có thể xem thêm ở phần mạch chia nhị phân chương 1, hình mạch khá phức tạp nên không được trình bày ở đây.

V.BỘ LOGIC VÀ SỐ HỌC

ALU là thành phần quan trọng của CPU trong máy tính, nó có thể thực hiện nhiều phép tính số học và logic dựa trên dữ liệu thường bao gồm phép cộng, trừ, and,or, exor, dịch chuyển, tăng giảm dần và cả phép nhân, chia. Ngoài ra cũng có một số ALU sản xuất ở dạng IC rời, tất nhiên chúng không thể làm đầy đủ các chức năng như ALU trong VXL. Sau đây, ta hãy xem qua 2 ALU rời hay dùng.

Hình 2.3.26 Khối ALU 74LS181

1.ALU 74LS181

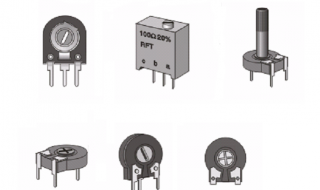

A0 – A3 : dữ liệu nhị phân 4 bit vào (A = A3A2A1A0)

B0 – B3 : dữ liệu nhị phân 4 bit vào (B= B3B2B1B0)

CYN : số nhớ ban đầu vào (tác động ở mức thấp)

S0 – S3 : Mã số chọn (S = S3S2S1S0) để chọn chức năng của ALU.

M điều khiển kiểu (chế độ) hoạt động logic (M =1) hay số học (M = 0).

Q0 – Q3 : dữ liệu nhị phân 4 bit ra tác động ở thấp (Q = Q3Q2Q1Q0).

CYN + 4 số nhớ ra (tác động thấp). Ở phép trừ nó chỉ dấu của kết quả :

o Logic 0 chỉ kết quả dương.

o Logic 1 chỉ kết quả âm ở dạng số bù 2.

Ngõ số nhớ vào Cn và ngõ số nhớ ra CYN+4 cho phép nối chồng nhiều IC 74LS181.

A = B : logic 1 ở ngõ vào này chỉ A = B, logic 0 chỉ A ≠ B.

G (carry generate output) và P (carry propagate input) : hai ngõ này được dùng khi nối chồng các IC 74LS181.

Hoạt động logic của 74181 được trình bày ở bảng chức năng dưới đây

2.ALU 74LS382

ALU 74LS/HC382 cũng là loại 4 bit nhưng có 3 ngõ chọn chức năng nên có ít chức năng logic số học hơn 74LS181. Nó cũng có ngõ vào số nhớ CN, ngõ ra số nhớ CYN+1 như 74LS181 nhưng có thêm ngõ ra chỉ báo tràn overflow trong lúc không có một số ngõ ra khác như 74LS181. Khi dùng số có dấu ngõ overflow sẽ lên 1 khi phép cộng hay trừ tạo số vượt quá số có dấu 4 bit. Ngõ số nhớ vào và số nhớ ra cũng còn dùng để nối chồng nhiều IC 74382.

Hình 2.3.27 Kí hiệu khối ALU 74LS382 và bảng hoạt động

Hình 2.3.19b Trừ 4 bit nối tiếp

Hình 2.3.19b Trừ 4 bit nối tiếp