I.Giới thiệu Mạch tách kênh

Bộ chuyển mạch phân kênh hay còn gọi là tách kênh, giải đa hợp (demultiplexer) có chức năng ngược lại với mạch dồn kênh tức là : tách kênh truyền thành 1 trong các kênh dữ liệu song song tuỳ vào mã chọn ngõ vào. Có thể xem mạch tách kênh giống như 1 công tắc cơ khí được điều khiển chuyển mạch bởi mã số. Tuỳ theo mã số được áp vào ngõ chọn mà dữ liệu từ 1 đường sẽ được đưa ra đường nào trong số các đường song song.

Các mạch tách kênh thường gặp là 1 sang 2, 1 sang 4, 1 sang 8, …Nói chung từ 1 đường có thể đưa ra 2n đường, và số đường để chọn sẽ phải là n. Mục dưới sẽ nói đến mạch tách kênh 1 sang 4

1 Mạch tách kênh 1 sang 4

Hình 2.2.9 Mạch tách kênh 1 sang 4

Hình 2.2.9 Mạch tách kênh 1 sang 4

Mạch tách kênh từ 1 đường sang 4 đường nên số ngõ chọn phải là 2

Khi ngõ cho phép G ở mức 1 thì nó cấm không cho phép dữ liệu vào được truyền ra ở bất kì ngõ nào nên tất cả các ngõ ra đều ở mức 0

Như vậy khi G = 0 BA = 00 dữ liệu S được đưa ra ngõ Y0, nếu S = 0 thì Y0 cũng bằng 0 và nếu S = 1 thì Y0 cũng bằng 1,tức là S được đưa tới Y0; các ngõ khác không đổi

Tương tự với các tổ hợp BA khác thì lần lượt ra ở S sẽ là Y1, Y2, Y3

Biểu thức logic của các ngõ ra sẽ là :

Y0 = G.B.A.S

Y1 = G.B.A.S

Y2 = G.B.A.S

Y3 = G.B.A.S

Từ đây có thể dùng cổng logic để thiết kế mạch tách kênh

Hình 2.2.10 Cấu trúc của mạch tách kênh 1 sang 4

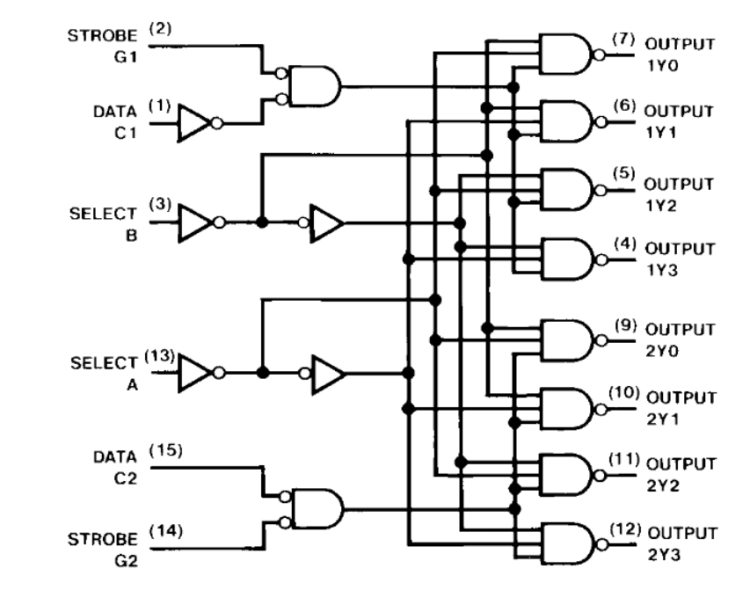

Ví dụ : Khảo sát IC 74LS155

Hình 2.2.12 Kí hiệu khối và chân ra của 74LS155

Trong cấu trúc của nó gồm 2 bộ tách kênh 1 sang 4, chúng có 2 ngõ chọn A0A1 chung, ngõ cho phép cũng có thể chung khi nối chân 2 nối với chân 15). Một lưu ý khác là bộ tách kênh đầu có ngõ ra đảo so với ngõ vào (dữ liệu vào chân 1 không đảo) còn bộ tách kênh thứ 2 thì ngõ vào và ngõ ra như nhau khi được tác động ( dữ liệu vào chân 14 đảo).

Cấu trúc logic của mạch không khác gì so với mạch đã xét ở trên ngoài trừ mạch có thêm ngõ cho phép

Bảng sự thật của 74LS155

Mạch tách kênh hoạt động như mạch giải mã

Nhiều mạch tách kênh còn có chức năng như 1 mạch giải mã. Thật vậy,vào dữ liệu S không được dùng như 1 ngõ vào dữ liệu nối tiếp mà lại dùng như ngõ vào cho phép còn các ngõ vào chọn CBA khi này lại được dùng như các ngõ vào dữ liệu và các ngõ ra vẫn giữ nguyên chức năng thì mạch đa hợp lại hoạt động như 1 mạch giải mã.

Tuỳ thuộc mã dữ liệu áp vào ngõ C B A mà một trong các ngõ ra sẽ lên cao hay xuống thấp tuỳ cấu trúc mạch. Như vậy mạch tách kênh 1:4 như ở trên đã trở thành mạch giải mã 2 sang 4 . Thực tế ngoài ngõ S khi này trở thành ngõ cho phép giải mã, mạch trên sẽ phải cần một số ngõ điều khiển khác để cho phép mạch hoạt động giải mã hay tách kênh; còn cấu tạo logic của chúng hoàn toàn tương thích nhau. Hình sau cho phép dùng mạch tách kênh 1 sang 4 để giải mã 2 sang 4

Hình 2.2.13 Mạch tách kênh hoạt động như mạch giải mã

Tương tự ta cũng có các loại mạch khác như vừa tách kênh 1:8 vừa giải mã 3:8, tách kênh 1:16/giải mã 4:16…

2.Một số IC giải mã tách kênh hay dùng

Khảo sát IC tách kênh/giải mã tiêu biểu 74LS138

- 74LS138 là IC MSI giải mã 3 đường sang 8 đường hay tách kênh 1 đường sang 8 đường thường dùng và có hoạt động logic tiêu biểu, nó còn thường được dùng như mạch giải mã địa chỉ trong các mạch điều khiển và trong máy tính.

- Sơ đồ chân và kí hiệu logic như hình dưới đây :

Hình 2.2.14 Kí hiệu khối và chân ra của 74LS138

- Trong đó

- A0, A1, A2 là 3 đường địa chỉ ngõ vào

- E1, E2 là các ngõ vào cho phép (tác động mức thấp)

- E3 là ngõ vào cho phép tác động mức cao

- O0 đến O7 là 8 ngõ ra (tác động ở mức thấp )

Hình 2.2.15 Cấu trúc bên trong 74LS138

- Hoạt động giải mã như sau :

Đưa dữ liệu nhị phân 3bit vào ở C, B, A(LSB), lấy dữ liệu ra ở các ngõ O0 đến O7; ngõ cho phép E2 và E3 đặt mức thấp, ngõ cho phép E1 đặt ở mức cao. Chẳng hạn khi CBA là 001 thì ngõ O1 xuống thấp còn các ngõ ra khác đều ở cao.

- Hoạt động tách kênh :

Dữ liệu vào nối tiếp vào ngõ E2, hay E3 (với ngõ còn lại đặt ở thấp). Đặt G = 1 để cho phép tách kênh. Như vậy dữ liệu ra song song vẫn lấy ra ở các ngõ O0 đến O7. Chẳng hạn nếu mã chọn là 001thì dữ liệu nối tiếp S sẽ ra ở ngõ O1 và không bị đảo.

- Mở rộng đường giải mã : 74LS138 dùng thêm 1 cổng đảo còn cho phép giải mã địa chỉ từ 5 sang 32 đường (đủ dùng trong giải mã địa chỉ của máy vi tính). Hình ghép nối như sau :

Hình 2.2.16 Ghép 4 IC 74LS138 để có mạch giải mã 5 đường sang 32 đường

Các IC giải mã tách kênh khác :

- Ngoài 74LS155 và 74LS138 được nói đến ở trên ra còn một số IC cũng có chức năng giải mã/tách kênh được kể ra ở đây là

- 74139/LS139 gồm 2 bộ giải mã 2 sang 4 hay 2 bộ tách kênh 1 sang 4, chúng có ngõ cho phép (tác động mức thấp) và ngõ chọn riêng

- 74154/LS154 bộ giải mã 4 sang 16 đường hay tách kênh 1 sang 16 đường

- 74159/LS159 giống như 74154 nhưng có ngõ ra cực thu để hở

- 74155/LS155 như đã khảo sát ở trên : gồm 2 bộ giải mã 2 sang 4 hay 2 bộ tách kênh 1 sang 4. Đặc biệt 74155 còn có thể hoạt động như 1 bộ giải mã 3 sang 8 hay tách kênh 1 sang 8 khi nối chung ngõ cho phép với ngõ vào dữ liệu nối tiếp và nối chung 2 ngõ chọn lại với nhau.

- 74156/LS156 giống như 74155 nhưng có ngõ ra cực thu để hở.

- Công nghệ CMOS cũng có các IC giải mã/tách kênh tương ứng như bên TTL chẳng hạn có 74HC/HCT138,…Hơn thế nữa nhiều IC họ CMOS còn cho phép truyền cả dữ liệu số lẫn dữ liệu tương tự. Một số IC được kể ra ở đây là

- 74HC/HCT4051 dồn/tách kênh tương tự số 1 sang 8 và ngược lại

- 74HC/HCT4052 dồn/tách kênh tương tự số 1 sang 4 và ngược lại

- 74HC/HCT4053 dồn/tách kênh tương tự số 1 sang 2 và ngược lại

Khảo sát IC 4051

- Khi dồn kênh dữ liệu vào chân COM OUT/IN, ra ở 3 kênh CHANNEL I/O từ 0 đến 7.

- Ngược lại, khi tách kênh thì dữ liệu song song vào các chân CHANNEL I/O 0 đến 7 và ra ở chân COM OUT/IN;

- 3 ngõ chọn là A, B, C.

- Chân INH (inhibit) cho phép dữ liệu được phép truyền ra.

- Hoạt động của IC được tóm tắt như bảng sau :

Hình 2.2.17 Chân ra 4051

- Cấu trúc logic mạch khá phức tạp như hình dưới đây

Hình 2.2.18 Cấu trúc mạch của 4051