I.Giới thiệu

Ở phần trước ta đã được biết đến các loại FF. Chúng đều có thể lưu trữ (nhớ 1 bit) và chỉ khi có xung đồng bộ thì bit đó mới truyền tới ngõ ra (đảo hay không đảo).

Bây giờ nếu ta mắc nhiều FF nối tiếp lại với nhau thì sẽ nhớ được nhiều bit. Các ngõ ra sẽ phần hoạt động theo xung nhịp ck. Có thể lấy ngõ ra ở từng tầng FF (gọi là các ngõ ra song song) hay ở tầng cuối (ngõ ra nối tiếp).

Như vậy mạch có thể ghi lại dữ liệu (nhớ) và dịch chuyển nó (truyền) nên mạch được gọi là ghi dịch.

Ghi dịch cũng có rất nhiều ứng dụng đặc biệt trong máy tính, như chính cái tên của nó: lưu trữ dữ liệu và dịch chuyển dữ liệu chỉ là ứng dụng nổi bật nhất

II.Cấu tạo

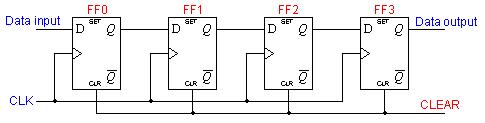

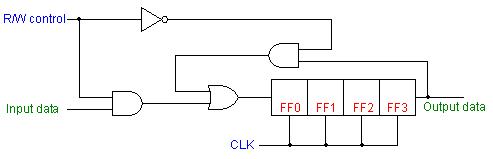

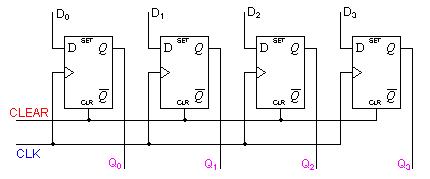

Ghi dịch có thể được xây dựng từ các FF khác nhau và cách mắc cũng khác nhau nhưng thường dùng FF D, chúng được tích hợp sẵn trong 1 IC gồm nhiều FF (tạo nên ghi dịch n bit). Hãy xem cấu tạo của 1 ghi dịch cơ bản 4 bit dùng FF D

Hình 2.1.Ghi dịch 4 bit cơ bản

III.Hoạt động

III.Hoạt động

Thanh ghi, trước hết được xoá (áp xung CLEAR) để đặt các ngõ ra về 0. Dữ liệu cần dịch chuyển được đưa vào ngõ D của tầng FF đầu tiên (FF0). Ở mỗi xung kích lên của đồng hồ ck, sẽ có 1 bit được dịch chuyển từ trái sang phải, nối tiếp từ tầng này qua tầng khác và đưa ra ở ngõ Q của tầng sau cùng (FF3). Giả sử dữ liệu đưa vào là 1001, sau 4 xung ck thì ta lấy ra bit LSB, sau 7 xung ck ta lấy ra bit MSB.

Nếu tiếp tục có xung ck và không đưa thêm dữ liệu vào thì ngõ ra chỉ còn là 0 (các FF đã reset : đặt lại về 0 hết. Do đó ta phải “hứng” hay ghim dữ liệu lại. Một cách làm là sử dụng 2 cổng AND, 1 cổng OR và 1 cổng NOT như hình dưới đây.

Hình 3.1.Cho phép chốt dữ liệu trước khi dịch ra ngoài

Dữ liệu được đưa vào thanh ghi khi đường điều khiển R/W control ở mức cao (Write). Dữ liệu chỉ được đưa ra ngoài khi đường điều khiển ở mức thấp (Read).

3.1.CÁC LOẠI THANH GHI DỊCH

Có nhiều cách chia loại thanh ghi dịch (SR)

- Theo số tầng FF (số bit) : SR có cấu tạo bởi bao nhiêu FF mắc nối tiếp thì có bấy nhiêu bit (ra song song). Ta có SR 4 bit, 5 bit, 8 bit, 16 bit …

- Có thể có SR nhiều bit hơn bằng cách mắc nhiều SR với nhau hay dùng công nghệ CMOS (các máy tính sử dụng SR nhiều bit)

- Theo cách ghi dịch có

- SISO vào nối tiếp ra nối tiếp

- SIPO vào nối tiếp ra song song

- PISO vào song song ra nối tiếp

- PIPO vào song song ra song song

- Theo chiều dịch có SR trái, phải, hay cả 2 chiều

- Theo mạch ra có loại thường và 3 trạng thái

- Loại vào nối tiếp ra song song và ra nối tiếp

- Loại vừa khảo sát ở mục 1 thuộc loại ghi dịch vào nối tiếp ra nối tiếp. Đây cũng là cấu trúc của mạch ghi dịch vào nối tiếp ra song song. Dữ liệu sẽ được lấy ra ở 4 ngõ Q của 4 tầng FF, vì chung nhịp đồng hồ nên dữ liệu cũng được lấy ra cùng lúc.

Hình 3.1.1 Mạch ghi dịch vào nối tiếp ra song song

Bảng dưới đây cho thấy làm như thế nào dữ liệu được đưa tới ngõ ra 4 tầng FF Loại được nạp song song (vào song song) ra nối tiếp và song song

Loại được nạp song song (vào song song) ra nối tiếp và song song

Bây giờ muốn đưa dữ liệu vào song song (còn gọi là nạp song song) ta có thể tận dụng ngõ vào không đồng bộ Pr và Cl của các FF để nạp dữ liệu cùng một lúc vào các FF. Như vậy có thể dùng thêm 2 cổng nand và một cổng not cho mỗi tầng. Mạch mắc như sau

Hình 3.1.2 Mạch ghi dịch nạp song song

Mạch hoạt động bình thường khi nạp song song ở thấp như đã nói. Khi nạp song song WRITE = 1 cho phép nạp

ABCD được đưa vào Pr và Cl đặt và xoá để Q0 = A, Q1 = B, … Xung ck và ngõ vào nổi tiếp không có tác dụng (vì sử dụng ngõ không đồng bộ Pr và Cl)

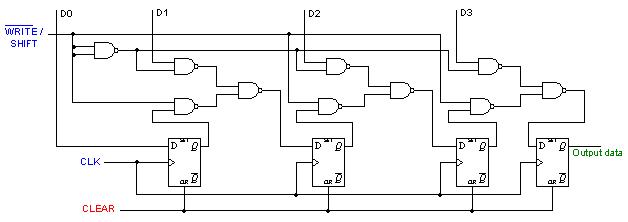

Một cách khác không sử dụng chân Pr và Cl được minh hoạ như hình dưới đây.Các cổng nand được thêm vào để nạp các bit thấp D1, D2, D3. Ngõ WRITE/SHIFT dùng để cho phép nạp (ở mức thấp) và cho phép dịch (ở mức cao). Dữ liệu nạp và dịch vẫn được thực hiện đồng bộ như các mạch trước.

Hình 3.1.3 Mạch ghi dịch nạp song song ra nối tiếp

Với mạch Hình 3.1.3 ngõ ra dữ liệu là nối tiếp, ta cũng có thể lấy ra dữ liệu song song như ở Hình 3.1.4, Cấu trúc mạch không khác so với ở trên. Dữ liệu được đưa vào cùng lúc và cũng lấy ra cùng lúc (mạch như là tầng đệm và hoạt động khi có xung ck tác động lên.

Hình 3.1.4 Mạch ghi dịch vào song song ra song song

Ghi dịch 2 chiều

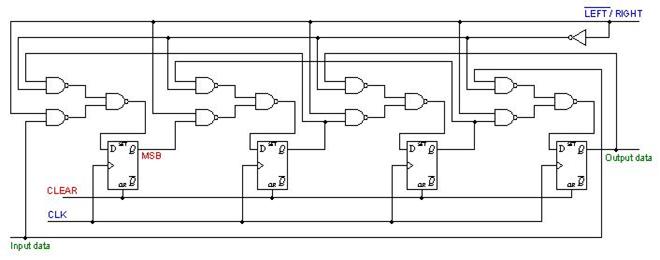

Như đã thấy, các mạch ghi dịch nói ở những phần trên đều đưa dữ liệu ra bên phải nên chúng thuộc loại ghi dịch phải. Để có thể dịch chuyển dữ liệu ngược trở lại (dịch trái) ta chỉ việc cho dữ liệu vào ngõ D của tầng cuối cùng, ngõ ra Q được đưa tới tầng kế tiếp, …. Dữ liệu lấy ra ở tầng đầu.

Để dịch chuyển cả 2 chiều, có thể nối mạch như hình dưới đây :

Hình 3.1.5 Mạch ghi dịch cho phép dịch chuyển cả 2 chiều

Hình 3.1.5 Mạch ghi dịch cho phép dịch chuyển cả 2 chiều

Với mạch trên, các cổng NAND và đường cho phép dịch chuyển dữ liệu trái hay phải. Bảng dưới đây minh hoạ cho mạch trên : dữ liệu sẽ dịch phải 4 lần rồi dịch trái 4 lần. Để ý là thứ tự 4 bit ra bị đảo ngược lại so với chúng ở trên. 3.2.MỘT SỐ IC GHI DỊCH

3.2.MỘT SỐ IC GHI DỊCH

Nhận thấy rằng các ghi dịch mô tả ở trên đều dùng các FF rời, rồi phải thêm nhiều cổng logic phụ để tạo các loại SR khác nhau. Trong thực tế ghi dịch được tích hợp sẵn các FF và đã nối sẵn nhiều đường mạch bên trong người sử dụng chỉ còn phải làm một số đường nối bên ngoài điều khiển các ngõ cho phép thôi. Các SR cũng được tích hợp sẵn các chức năng như vừa có thể dịch trái dịch phải vừa vào nối tiếp vừa nạp song song.

Ở đây là một số ghi dịch hay được dùng :

Liệt kê

7494 : 4bit vào song song, nối tiếp; ra nối tiếp

7495/LS95 : 4 bit, vào song song/nối tiếp; ra song song; dịch chuyển trái phải

7495/LS96 : 5 bit, vào nối tiếp/song song; ra song song nối tiếp

74164/LS164 : 8 bit vào song song ra nối tiếp

74165/LS765 : 8 bit, vào song song/nối tiếp; ra nối tiếp bổ túc

74166/LS166 : 8 bit; vào song song/nối tiếp; ra nối tiếp; có thể nạp đồng bộ

74194/LS194 : 4 bit vào song song/nối tiếp; ra song song; nạp đồng bộ dịch chuyển trái phải

74195/LS195 : 4 bit, vào song/nối tiếp; ra song song; tầng đầu vào ở JK

74295/LS295 : như 74194/LS194 nhưng ra 3 trạng thái

74395/LS295 : 4 bit vào song song; ra song song 3 trạng thái

74LS671/672 : 4 bit có thêm chốt

74LS673/674 : 16 bit

Khảo sát ghi dịch tiêu biểu 74/74LS95 Hình 3.2.1 Sơ đồ chân ra 74LS95

Hình 3.2.1 Sơ đồ chân ra 74LS95

Sơ đồ cấu tạo và bảng hoạt động của IC như hình trên. Các chế độ hoạt động của nó như sau :

Nạp nối tiếp

Đưa dữ liệu vào tầng đầu Q0

Đặt điều khiển chọn ở mức thấp

Khi có ck1 hay ck2 thì dữ liệu sẽ lần lượt nạp vào ghi dịch và sẽ được đưa tới các tầng sau

Nạp song song

Dữ liệu vào ở 4 ngõ ABCD

Đưa điều khiển kiểu lên cao

Khi có ck1 hay ck2 thì dữ liệu sẽ được nạp vào đồng thời các tầng của ghi dịch ở cạnh lên đầu của xung ck.

IV.ỨNG DỤNG

Thanh ghi dịch đóng vai trò cực kì quan trọng trong việc lưu trữ, tính toán số học và logic. Chẳng hạn trong các bộ vi xử lí, máy tính đều có cấu tạo các thanh ghi dịch; trong vi điều khiển (8051) cũng có các ghi dịch làm nhiều chức năng hay như trong nhân chia, ALU đã xét ở chương 2 ghi dịch cũng đã được đề cập đến. Ở đây không đi vào chi tiết mà chỉ nói khái quát ngắn gọn về ứng dụng của chúng.

1.Lưu trữ và dịch chuyển dữ liệu

Đây là ứng dụng cơ bản và phổ biến nhất của chúng. Ghi dịch n bit sẽ cho phép lưu trữ được n bit dữ liệu một thời gian mà chừng nào mạch còn được cấp điện. Hay nói cách khác dữ liệu khi dịch chuyển đã được trì hoãn một khoảng thời gian, nó tuỳ thuộc vào :

- Số bit có thể ghi dịch (số tầng FF cấu tạo nên ghi dịch)

- Tần số xung đồng hồ

2.Tạo kí tự hay tạo dạng song điều khiển

Ta có thể nạp vào ghi dịch, theo cách nạp nối tiếp hay song song, một mã nhị phân của một chữ nào đó (A, B, …) hay một dạng sóng nào đó.

Sau đó nếu ta nối ngõ ra nối tiếp của ghi dịch vòng trở lại ngõ vào nối tiếp thì khi có xung ck các bit sẽ dịch chuyển vòng quanh theo tốc độ của đồng hồ.

Cách này có thể điều khiển sáng tắt của các đèn (sắp xếp trên vòng tròn hay cách nào khác) Như mô phỏng sau là dạng sáng tắt của đèn led.

Với tải cổng suất thì cần mạch giao tiếp công suất như thêm trans, rờ le, SCR,… đã nói ở chương 1 cũng sẽ được dùng.

Cũng có thể tạo ra dạng sóng tín hiệu tuần hoàn cho mục đích thử mạch bằng cách này. Ta có thể thay đổi dạng sóng bằng cách thay đổi mã số nhị phân nạp cho ghi dịch, và thay đổi tần số xung kích ck được cấp từ mạch dao động ngoài từ 0 đến 200MHz tuỳ loại mạch ghi dịch.

Hình 3.1 Tạo dạng sóng điều khiển bởi ghi dịch

3.Chuyển đổi dữ liệu nối tiếp sang song song và ngược lại

Các máy tính hay các bộ vi xử lí khi giao tiếp với nhau hay với các thiết bị ngoài thường trao đổi dữ liệu dạng nối tiếp khi giữa chúng có một khoảng cách khá xa.

Ngoài cách dùng các bộ dồn kênh tách kênh ở 2 đầu truyền mà ta đã nói ở chương 2 thì ghi dịch cũng có thể được dùng.

Các ghi dịch chuyển song song sang nối tiếp sẽ thay thế cho mạch dồn kênh và các ghi dịch chuyển nối tiếp sang song song sẽ thay thế cho mạch tách kênh.

Bên cạnh ghi dịch, cũng cần phải có các mạch khác để đồng bộ, chống nhiễu, rò sai… nhằm thực hiện quá trình truyền nối tiếp hiệu quả.

hình 3.2.11 Truyền dữ liệu nối tiếp

4.Bus truyền dữ liệu

Bây giờ liệu với 8 đường dữ liệu song song vừa nhận được từ tách kênh đó (còn gọi là 1 byte), ta có thể dùng chung cho nhiều mạch được không? Sở dĩ có yêu cầu đó là vì trong máy vi tính có rất nhiều mạch liên kết với nhau bởi các đường dữ liệu địa chỉ gồm nhiều bit dữ liệu 8, 16, 32… mà ta đã biết đến nó với cái tên là bus.

Vậy bus chính là các đường dữ liệu dùng chung cho nhiều mạch (chẳng hạn bus giữa các vi xử lí, các chíp nhớ bán dẫn, các bộ chuyển đổi tương tự và số,…

Chỉ có một đường bus mà lại dùng chung cho nhiều mạch, do đó để tránh tranh chấp giữa các mạch thì cần phải có một bộ phận điều khiển quyết định cho phép mạch nào được thông với bus, các mạch khác bị cắt khỏi bus. Vậy ở đây thanh ghi hay các bộ đệm 3 trạng thái được dùng

Hình dưới minh hoạ cho đường bus 8 bit nối giữa vi xử lí với bộ đếm 8 bit, bàn phím, và bộ 8 nút nhấn

Giả sử rằng cả thiết bị đều cần giao tiếp với vi xử lí, nhưng chỉ có một đường truyền nếu tất cả đồng loạt đưa lên thì có thể bị ảnh hưởng lẫn nhau giữa các dữ liệu, và thông tin nhận được là không chính xác.

Do đó ở đây vi xử lí sẽ quyết định: chẳng hạn nó đặt ngõ OE1 cho phép bộ đếm cho mạch đếm đưa dữ liệu lên bus còn chân OE2 và OE3 ngưng làm dữ liệu từ bàn phím và nút nhấn bị ngắt (chờ) tức ngõ ra các bộ đệm hay thanh ghi 3 trạng thái ở trạng thái tổng trở cao.

Tương tự khi vi xử lí cần giao tiếp với các mạch khác. Với tốc độ xử lí hàng trăm hàng ngàn MHz thì việc dữ liệu phải chờ là không đáng kể do đó giữa các thiết bị giao tiếp với nhau rất nhanh và dường như đồng thời.